Menda Srikanth, 2024, 12:5 ISSN (Online): 2348-4098 ISSN (Print): 2395-4752

An Open Access Journal

# Decoder and Multiplexer Comparison with Mixed Logic and CMOS Logic with 90nm Technology

P.G Scholor Menda Srikanth, Assistant Professor P. S. N Bhaskar

Sanketika Vidya Parishad Engineering College, Visakhapatnam, India

Abstract- Mixed logic designs take prioritized place in logic design approaches which will give a simplified mechanism for the analysis of digital circuits. Also, a mixed logic implementation gives clear idea with regards to the activity of a circuit. Here in this, introduced mixed logic designs like pass transistor dual value logic (DVL), transmission gate logic (TGL), static CMOS. By using CMOS technology, it requires 20 transistors to design 2:4-line decoder but by using mixed logic we can design the same 2:4-line decoder with the use of 14transistors (14T) only. Introducing mixed logic approach a 4:1 MUX was designed by using 2:4-line decoder of mixed logic design. This new approach gives the better operating speed, low power consumption compared to conventional logic design by reducing the transistors activity and simulations are carried out using tanner EDA tools.

Keywords- Mixed logic, Low power MUX, Line decoder, Transmission gate logic (TGL), Dual value logic (DVL) & Static CMOS

### I. INTRODUCTION

In most of the integrated circuits, we generally prefer Static CMOS because of complementary nMOS and pMOS networks which results in good performance as well as resistance to noise and device variation. But by using CMOS technology, it requires 20 transistors to design 2:4-line decoder but by using mixed logic we can design the same 2:4-line decoder with the use of 14transistors (14T) only. Pass transistor logic (PTL) was developed as an alternative to CMOS logic. The main difference between the CMOS logic and PTL design is how the inputs are applied. In the PTL inputs are applied on the gates as well as source/drain terminals. PTL can be designed using either of nMOS and pMOS. The DVL has advantages over the PTL such as full swing operation while also maintaining reduced transistor count. A pair of nMOS and pMOS connected in parallel are called TGL. 2-4 Line Decoder: 2-bit input line decoder has 4-bit output. In conventional static CMOS line decoder uses 2 NOT gates and 4

AND gates. Instead of using AND gates we can use NAND gates as they are universal gates. So, for this design it uses 20 transistors for 2–4-line decoder.

4x1 Multiplexer: It consists of 4 input lines and 1 output. The selection line decides which inputs should go to the output. The conventional CMOS design for 4x1 mux uses 2 NOT gates, 4 3-input AND gates and 1 4-input OR gate. The total transistor count for this conventional design 4x1 line multiplexer is 46 Transistors.

### II. MIXED LOGIC

### 1. Cmos Logic

A static CMOS circuit is composed of two networks: Pull-up network (PUN) - a set of PMOS transistors connected between Vcc and the output line. Pull-down network (PDN) - a set of NMOS transistors connected between GND and the output line The main advantage of CMOS over NMOS and BIPOLAR technology is the much smaller power dissipation.

© 2024 Menda Srikanth. This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly credited.

Unlike **NMOS BIPOLAR** or circuits. Complementary MOS circuit has almost no static power dissipation. Power is only dissipated in case the circuit actually switches. This allows integrating more CMOS gates on an IC than in NMOS or bipolar technology, resulting in much better performance. Complementary Metal Oxide Semiconductor transistor consists of P-channel MOS (PMOS) and N-channel MOS (NMOS).

# 2. Transmission Gate Logic

The PMOS and the NMOS transistors present in the circuit are always connected in parallel which are managed via complementary signals. Combining an NMOS and PMOS back-to-back will make the resulting transmission gates to pass a good active low "0" and also a good active high "1" signal.

# 3. Dual Value Logic

The Pass transistor logic is required to reduce the transistors for implementing logic by using the primary inputs to drive gate terminals, source and drain terminals. In complementary CMOS logic primary inputs are allowed to drive only gate terminals. There are several pass transistor logics are developed. The best possible pass transistor logic is Dual Value Logic which is to be consider for our comparisons. DVL is basically derived from DPL. The elimination of redundant branches and rearrangement of signals allows the DVL is advantageous compared to DPL. The speed compensation degrades due to PMOS transistors and straightforward full swing operation make it possible to use DVL logic style.

## III. IMPLEMENTATION

1. Decoder Using CMOS logic

Figure 1: 20T CMOS Decoder

Figure 2: 14T mixed logic Decoder

The mixed logic design for decoder is shown in above figure 2. The mixed logic decoder is designed with 14T. It Reduces transistors count. Hence, low power consumption, delay is reduced and smaller area can be achieved.

# 4. 4:1 MUX Using CMOS logic

The 4:1 Mux using CMOS logic is shown in above figure 3. To design CMOS 4:1 MUX total 46 transistors were used. The 46T MUX using AND and OR gates consume more power due to a greater number of transistors

Figure 3: 46T CMOS 4:1 MUX.

# 5. 4:1 MUX Using Mixed Logic

Figure 4: 38T mixed logic 4:1 MUX

The 4:1 MUX using mixed logic is shown in above figure 4. The design has totally 38 transistors using 2:4-line decoder mixed logic style. Instead of AND and OR gates NAND gates are used to design the mixed logic style for 4:1 MUX. It reduces the transistors count when compared to conventional CMOS. Hence, power consumption is low and delay is reduced.

### IV. SIMULATION RESULTS

Figure 5: Input and Output waveforms of CMOS Based Decoder using NAND gates

Figure 6: Input and Output waveforms of mixed logic Based Decoder using NAND gates

Figure 7: Input and Output waveforms of CMOS Based 4:1 MUX using AND and OR gates

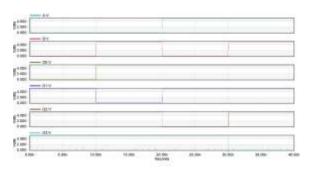

Figure 8: Input and Output waveforms of mixed logic Based 4:1 MUX

# **Comparison Table**

Table 1: Comparison between CMOS and Mixed logic styles

| Logic | No. of<br>Transistors | SUPPLY | POWER    | DELAY     |

|-------|-----------------------|--------|----------|-----------|

| CMOS  | 46                    | 5V     | 4.6893uw | 17.0270ns |

| MIXED | 38                    | 5V     | 2.1655uw | 10.0244ns |

# V. FUTURE SCOPE AND CONCLUSION

### 1. Conclusion

This Paper introduced a mixed logic design for a multiplexer aiming for low power and reduced area in consideration. By using a line decoder, we tried to achieve this low power MUX by using mixed logic design. And instead of AND, OR gates we used NAND gates to further reduce the Transistor count, power consumption and area. The proposed design is compared to the conventional CMOS design. The line decoder is designed with TGL, DVL and the NAND gates are static CMOS, by

combining these 3 logics designs we can have a mixed logic design.

multiplier with kogge-stone adder, Int. J. Innov. Technol. Explor. Eng. 8 (6) (2019) PP.92-96.

# 2. Future Scope

In future the mixed logic design can be implemented in various digital circuits and the sequential circuits. As the proposed designs have proven to work efficiently in terms of various performance parameters thus; the more effective results are expected to be obtained while incorporating these circuits to implement other complex systems in the field of low power VLSI design.

### REFERENCES

- 1. N.H.E. Weste, D.M. Harris, "CMOS VLSI Design, a Circuits and Systems Perspective," 4th ed., 2011: Addison-Wesley.

- R. Zimmermann, W. Fichtner, Low-power logic styles: CMOS versus pass transistor logic, IEEE J. Solid State Circuits 32 (7) (1997) 1079–1090.

- 3. D. Balobas, N. Konofaos, Design of low-power High-performance 2–4 and 4–16 mixed-logic line decoders, IEEE Trans. Circuits Syst. II: Express Briefs 64(2)(2017)176–180, https://doi.org/10.1109/TCSII.2016.255502.

- P.K. Mariya, V. Agarwal, R.S. Ernest Ravindran, T. Hareesh, B. Harsha, G.V. Kalayan, Design of lowpower, area efficient 2–4 and 4–16 mixed-logic line decoders, J. Adv. Res. Dyn. Control Syst. 11 (2019) 2961–2971.

- K. Yano et al., A 3.8-ns CMOS 16x16-b multiplier using complementary pass transistor logic, IEEE J. Solid-State Circuits 25 (1990) 388– 393.

- D. Markovic´, B. Nikolic´, V.G. Oklobdzˇija, A general method in synthesis of passtransistor circuits, Microelectron. J. 31 (11-12) (2000) 991– 998.

- P. Ramakrishna, K. Hari Kishore, G. Chandana, Implementation of low power and area efficient 7-bit flash analog to digital converter, J. Comput. Theor. Nanosci. 16 (5) (2019) 2213– 2217.

- 8. S. Rooban, S. Saifuddin, S. Leelamadhuri, S. Waajeed, Design of fir filter using wallace tree