# Review and Design a Low Power Configurable Adder for CORDIC Architecture Using Carry Select Adder

M.Tech.Scholar Harshit Tiwari, Dr. Tarun Verma

Department of Electronics & Communication Engineering Lakshmi Narain College Of Technology, Bhopal, (M.P.) harshittiwari 18@gmail.com

Abstract- The goal of this research work is to develop CORDIC processors, as well as various digital circuits such as sine-cosine generators, multiplication-division function generators, exponential and hyperbolic function generators, utilizing the VHDL language and the conventional and scale-free CORDIC algorithms. Also, using VHDL, build a finite impulse response filter, an infinite response filter, and several window function generators based on the traditional CORDIC algorithm and the scale-free CORDIC method, then implement all of these solutions on an FPGA.

Keywords - CORDIC algorithms, FPGA, VHDL language etc.

# I. INTRODUCTION

Because microprocessors provide single cycle multiply-assemble commands and distinctive addressing modes, they have been a dominant processor in the field of digital signal processing for a long time. These processors are versatile and inexpensive, but their speed is insufficient for truly powerful DSP operations.

The progress of reconfigurable logic computers necessitates the development of dedicated hardware solutions with faster speeds and lower costs that are comparable to the attractiveness of traditional software. However, for systems that rely on a microprocessor, optimal algorithms do not always translate well into hardware architecture.

So a hardware-efficient algorithm is constructed as a series of iterative explications for trigonometric and other transcendental functional operations evaluations that rely just on shifts and adds operations. Coordinate Rotation Digital Computer, or CORDIC, is the name given to this shift-add method. For DSP workloads, processors built using the CORDIC algorithm have a faster speed. As a result, processors based on the CORDIC theorem can readily replace microprocessors.

There have been various improvements in the research area of rapid VLSI architectonics for realtime Digital signal processing (DSP) algorithms in recent years, which have provided the inventor with significant motivation for developing contrivances into hardware architecture. Trigonometric operations are computed using a variety of methods, including table lookups and polynomial approximations or expansions.

However, the procedures indicated above necessitate a large number of multiplications and additions/ subtractions. Aside from these methods, a, for estimating these fundamental functions, which is faster than software explanations. These are operations such as repetitive pseudo subtraction, division, and pseudo addition, as well as multiplication. The CORDIC theorem was utilized to reduce the required number of multiplication and addition/subtraction operations.

## **II. RELATED WORK**

Current methods for describing the power consumption of adders assume that the data sources are completely random. However, the sources of data generated by sensible applications are not random, and in fact include a lot of structure.

© 2021 Harshit Tiwari. This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly credited.

International Journal of Science, Engineering and Technology

#### An Open Access Journal

Information bits will most likely remain in the same legitimate states from expansion to expansion than would be expected by chance, and bits, especially the most essential bits, will most likely be indistinguishable from their neighbours [1].

Power management is an important component of microchip design that is becoming increasingly important. A precise understanding of the origins and severity of power scattering inside a chip may influence a designer to make specific choices between speed and power, whereas a less precise understanding may result in decisions that are more detrimental to overall execution. Clearly, a precise depiction of how a microprocessor distributes control is essential to superb outline. Circuit mobility is by and large one of the most important aspects in vitality distribution [3].

The part and power dissipation are summarized at comparable proportions with detail to the RCA and BEC methods, according to Ramakrishna Reddy et al[1]It is seen from the outcomes that the part and power dissipation are summary at similar proportions with detail to the RCA and BEC methods.

When SHM is employed at the second level of the second block in 16-bit SQRT CSLA, the power dissipation is decreased by 6.4 percent and the expanse is lowered by 13.5 percent.

P. The power and latency of all of these adder architectures are designed for different input voltages, according to **Saxena et al [2].** The results show that Modified SQRT BK CSA outperforms all extra adder architectures in terms of power while incurring a minor speed cost. Tanner EDA tool was used to synthesis the designs at 45nm technology.

S. In comparison to conventional full adder designs, the suggested hybrid full adder consumes less power and energy.

**A. Simon et al [3]** Finally, using the proposed full adder, a four operand, eight-bit carry-save adder with a concluding carry propagate adder was applied, and its presentation was evaluated based on its average power consumption in 90 nm technology.

**R. Katreepalli et al. [4]** This suggested work evaluates the proposed designs' performance in

terms of latency, power consumption, and hardware. To demonstrate its efficiency, the results are evaluated and compared to existing fast adder architectures. In terms of power-delay product (PDP) and hardware overhead, the simulation results show that the suggested architecture provides two benefits.P. The performance of a reversible carry select adder is proven in terms of Ancilla, Quantum Cost, and Garbage outputs in this study by

**S. K. Reddy et al [5].** The revocable carry choose adder, which detects single stuck-at faults in a circuit, now has an online testing feature. In terms of Quantum cost and Ancilla, the proposed technique is superior to a simple carry choose adder.

**S. Bhatnagar et al. [6]** propose a method for CSA conniving using BEC-1 and a GDI-enabled D-latch applied using Tanner tool. The existence of power and density of MOSFETs has been linked, and a well-organized CSA has been analyzed.

**T. Yang and colleagues. [7]** By dynamically determining the length of the carry propagation, the proposed system can flexibly alter the length of the carry propagation to content the quality supplies. When compared to a conservative ripple carry adder and a typical carry look-ahead adder, the proposed 16-bit adder has a low power usage.

**H. Mahdavi et al.[9]** also show that for applications like the fast Fourier transform (FFT), where the initial angles are known ahead of time, the proposed look-ahead BSD-CORDIC with the posibit-negabit encoding, as our best presenting structure, improves speed, power consumption, and area overhead significantly.

**Y. N. Nirmala et al. [10]** used a hardware implementation method called CORDIC to combine two processors into a coprocessor, which helps with clock cycle reduction, high performance, and low cost. VHDL is used to describe the design, while modals are used to simulate it.

# III. PROPOSED METHODOLOGY

Design Aspects of the Scale–Free CORDIC Architecture Disintegration of angle of rotation into micro rotations- The angle of rotation is employed in conventional CORDIC as follows (i) the fundamental angles are elucidate according to the 2 - i where i is the count of iteration and read only memory (ROM) is used as a storage bank for the fundamental angles, (ii) the micro-rotation analogous to all the fundamental angles are executed in clock-wise or anti clock-wise, and (iii) every elementary angle is non replicate., but in scale free CORDIC Processor the micro rotations are rotated unidirectional with multiple times corresponding to the initial shifts and for other shifts non-replicate iterations are incorporated.

For extermination of the ROM which is used for restoring of elementary angles and for minimization of the hardware describe the elementary angles as:  $\alpha i = 2 - si$  where si is the numeral of shifts for ith iteration. (b)The most significant one location shows the bit location of the one (1) in an input string of bits initiated from most significant bit (MSB).The MSO location identifier(MSO-LI) produces an n-bit output for a 2 *n*bit input string. It is used for obtaining the shift index. si = N - M, N is the word length of the input data and M is the location of the most significant bit (one) in N input string. (c) The largest elementary angle is decided by the order of approximation of Taylor series.

For third order of approximation the basic shift and the largest elementary angle are to be: where I is the word-length. For 16 bit word length, sb = 2.854.According to the desired accuracy, researcher can either select sb = 2 or sb=3. Any rotation angle  $\theta$  is expressed as: where  $si \ge sb$  and n = n1 + n2, n is the total no of iterations 'n' is a constant.

The numeral of iteration for third orders Taylor series approximately is seven

$$s_{b} = \left\lfloor \frac{l - \log 2(4!)}{4} \right\rfloor$$

$$\alpha_{max} = 2^{-s_{b}}$$

$$\theta = n_{1} \cdot \alpha_{max} + n_{2} \cdot \sum \alpha_{si}$$

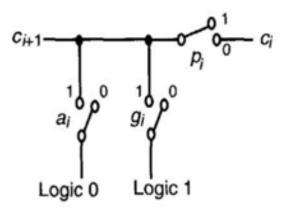

#### 1. Carry-Look Ahead Adder:

The carry forward adders figures accumulate create motions and also group engenders indicators to avoid waiting for a swell to determine whether or not the primary gathering produces a carry [8]. Genuine operand digits aren't important in terms of carry proliferation or the design of a carry arrangement. What matters is whether a carry is produced, spread, or removed in a particular situation [9].

The produce, proliferate, and demolish signals are represented by the following logic conditions as a result of parallel expansion: Assuming that the above signs are created and made accessible, whatever remains of the carry organize configuration can be based on them and turn out to be completely free [10]. The carry repeat can be composed as follows Typical the carry-look ahead adder is expressed using the prior indications.

Fig 1. Typical carry-look ahead adder.

CLAA [11] can give carries faster due to additional hardware that provides parallel carry bits at any point where the input changes. This system uses carry sidestep logic to speed up carry engendering.

A more advanced way for dealing with control estimation is to reenact the circuit hinder [12] being referred to for some arrangement of data sources. Running enough data vectors to ensure that the results are sufficiently precise can be timeconsuming, but there are a number of approaches that can be used to speed up or inexact the procedure if the experimenter accepts that the contributions to the adder are measurably independent of one another, and progressively if the extra suspicion that the data sources are not measurably independent of one another. These suspicions [13] and estimates are commonly utilized, and authors of adders generally understand that each item of data represents a.

Once the action components of the various doors have been addressed, an indistinguishable condition from the constant movement factor technique can be utilized to quantify control use [14].

International Journal of Science, Engineering and Technology

An Open Access Journal

As seen, there are large changes in quantifiable behavior between bits in the adder's upper and lower spans. The impact of these differences on the vitality utilization of various domains of an adder is a significant angle for numerous models [15].

This viewpoint is effective for generating a half breed adder by incorporating diverse designs into the adder's domains that are most appropriate for them, with the goal of increasing overall competence. For example, expect adder a used 75% of its vitality in bits0-15, while adder B used equivalent amounts of vitality in bits0-15 and bits16-31 [16].

If adders An and B have the same vitality [17] defer item and can be joined so that the deferral of a half and half adder is the mean [18] of the postponements of each separately, then replacing the initial 16bits of adder A with the logic from adder B will result in an adder with a vitality defer item 25% lower than its part adders [20].

It may be desirable to combine [23] two adders with distinct vitality defer items, or two adders whose deferrals do not include straightly, if the appropriation [21] of vitality utilization in two adders differs noticeably [22].

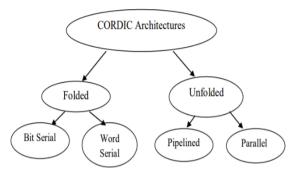

## 2. Architectures Cordic

The CORDIC theorem is used to create a variety of CORDIC structures. The CORDIC architectures are divided into two halves, one folded and the other unfolded. Architectonics are usually separated into two portions, one folded and one unfolded, and these architectures are guided by the application of three iterative mathematical expressions.

The CORDIC theorem-based three difference equations are realized in VLSI hardware, and all redundancy cycles are temporally multiplexed into an operating unit, resulting in Folded Architecture. The bit-serial and word-serial architectures are two types of folding architecture proposed by the operational unit realization, depending on whether the logic is chosen for one-bit or one word of CORDIC algorithm redundancy.

Fig 2. Classifications of the CORDIC Architecture.

# **IV. CONCLUSION AND FUTURE WORK**

The thesis examines the CORDIC Algorithm and its implementation. The CORDIC algorithm was used to implement the sine, cosine, tan-1, multiplication, and division functions with a reduced number of iterations. Wireless applications and mobile communications, as well as software defined radio services, make use of these fundamental functions.

Configured and confirmed are the 10-bit CORDIC bit parallel iterative processor, bit parallel unrolled CORDIC processor, and bit serial iterative CORDIC processor. The simulation ramifications of different CORDIC processors have also been addressed in terms of propagation latency and percentage inaccuracy.

In comparison to bit serial processors, the bit parallel CORDIC processor offers better agility, according to the analysis. The CORDIC processor, which is a scalefree pipelined processor, has been investigated. In comparison to the standard CORDIC design, the scale free CORDIC processor has no combinational path delay.

## REFERENCE

- Ramakrishna Reddy and M. Parvathi, "Efficient carry select adder using 0.12µm technology for low power applications," 2013 International Conference on Advances in Computing, Communications and Informatics (ICACCI), 2013, pp. 550-553, doi: 10.1109/ICACCI.2013.6637231.

- [2] P. Saxena, "Design of low power and high speed Carry Select Adder using Brent Kung adder," 2015 International Conference on VLSI Systems, Architecture, Technology and Applications (VLSI-SATA), 2015, pp. 1-6, doi: 10.1109/VLSI-SATA.2015.7050465.

- [3] S. A. Simon and S. S, "Implementation of Carry Save Adder Using Novel Eighteen Transistor Hybrid Full Adder," 2020 International Conference on Power Electronics and Renewable Energy Applications (PEREA), 2020, pp. 1-4, doi: 10.1109/PEREA51218.2020.9339799.

- [4] R. Katreepalli and T. Haniotakis, "High Speed Power Efficient Carry Select Adder Design," 2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2017, pp. 32-37, doi: 10.1109/ISVLSI.2017.16.

- [5] P. S. K. Reddy and G. Saini, "Design of Carry Select Adder with Online Testability Using Reversible Gates," 2019 4th International Conference on Recent Trends on Electronics, Information, Communication & Technology (RTEICT), 2019, pp. 486-490, doi: 10.1109/RTEICT46194.2019.9016873.

- [6] S. Bhatnagar, V. Agrawal and R. Marwal, "Analysis of MOSFET density and reduction in power consumption of Carry Select Adder using gate diffusion input," 2016 International Conference on Recent Advances and Innovations in Engineering (ICRAIE), 2016, pp. 1-6, doi: 10.1109/ICRAIE.2016.7939558.

- [7] T. Yang, T. Ukezono and T. Sato, "A low-power configurable adder for approximate applications," 2018 19th International Symposium on Quality Electronic Design (ISQED), 2018, pp. 347-352, doi: 10.1109/ISQED.201 8.8357311.

- [8] S. Kanekar and P. K. Dakhole, "Radix-10 multiplier implementation with carry select adder using Verilog," 2017 International Conference on Innovations in Information, Embedded and Communication Systems (ICIIECS), 2017, pp. 1-4, doi: 10.1109/ICIIECS.2017.8275857.

- [9] B. S. Premananda, M. K. Chandana, K. P. Shree Lakshmi and A. M. Keerthi, "Design of low power 8-bit carry select adder using adiabatic logic," 2017 International Conference on Communication and Signal Processing (ICCSP), 2017, pp. 1764-1768, doi: 10.1109/ICCS P.2017.8286696.

- [10] Y. N. Nirmala, K. C. Shilpa, S. B. Umesh and H. Kumar, "Design of CORDIC coprocessor for sparc V8," 2017 International Conference on Computing Methodologies and Communication (ICCMC), 2017, pp. 200-203, doi: 10.1109/ICCMC .2017.8282674.

- [11] H. Mahdavi and S. Timarchi, "Improving Architectures of Binary Signed-Digit CORDIC

With Generic/Specific Initial Angles," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 67, no. 7, pp. 2297-2304, July 2020, doi: 10.1109/TCSI.2020.2978765.

- [12] Kabra N.K., Patel Z.M. (2019) Low-Power and High-Speed Configurable Arithmetic and Logic Unit. In: Saini H., Singh R., Kumar G., Rather G., Santhi K. (eds) Innovations in Electronics and Communication Engineering. Lecture Notes in Networks and Systems, vol 65. Springer, Singapore. https://doi.org/10.1007/978-981-13-3765-9\_37.

- [13] Sivanandam K., Kumar P. (2018) Low-Power High-Performance Multi transform Architecture Using Run-Time Reconfigurable Adder for FPGA and ASIC Implementation. In: Muttoo S. (eds) System and Architecture. Advances in Intelligent Systems and Computing, vol 732. Springer, Singapore. https://doi.org/10.1007/978-981-10-8533-8\_7.

- [14] Hanif M.A., Hafiz R., Shafique M. (2019) Configurable Models and Design Space Exploration for Low-Latency Approximate Adders. In: Reda S., Shafique M. (eds) Approximate Circuits. Springer, Cham. https://doi.org/10.1007/978-3-319-99322-5\_1.

- [15] Porto, R., Correa, M., Goebel, J. et al. UHD 8K energy-quality scalable HEVC intra-prediction SAD unit hardware using optimized and configurable imprecise adders. J Real-Time Image Proc 17, 1685–1701 (2020). https://doi.o rg/10.1007/s11554-019-00934-2.

- [16] Alhammadi, A.A., Nazzal, T.B. & Mahmoud, S.A. A CMOS EEG detection system with a configurable analog front-end architecture. Analog Integr Circ Sig Process 89, 151–176 (2016). https://doi.org/10.1007/s10470-016-0826-x.

- [17] Diniz, C.M., Fonseca, M.B., da Costa, E.A.C. et al. evaluating the use of adder compressors for power-efficient HEVC interpolation filter architecture. Analog Integer Circ Sig Process 89, 111–120 (2016). https://doi.org/10.1007/s10470-016-0765-6.

- [18] Mami, S., Saad, I.B., Lahbib, Y. et al. Enhanced Configurable DCT Cordic Loeffler Architectures for Optimal Power-PSNR Trade-Off. J Sign Process Syst 90, 371–393 (2018). https://doi.org /10.1007/s11265-017-1245-7.

- [19] Rammohan, S.R., Jayashri, N., Bivi, M.A. et al. High performance hardware design of compressor adder in DA based FIR filters for hearing aids. Int J Speech Technol 23, 807–814

An Open Access Journal

(2020). https://doi.org/10.1007/s10772-020-09759-y.

- [20] Ahmad, F., Ahmed, S., Kakkar, V. et al. Modular Design of Ultra-Efficient Reversible Full Adder-Subtractor in QCA with Power Dissipation Analysis. Int J Theor Phys 57, 2863–2880 (2018). https://doi.org/10.1007/s10773-018-3806-3.

- [21] Esposito, D., De Caro, D., Di Meo, G. et al. Low-Power Hardware Implementation of Least-Mean-Square Adaptive Filters Using Approximate Arithmetic. Circuits Syst Signal Process 38, 5606– 5622 (2019). https://doi.org/10.1007/s00034-019-01132-y.

- [22] Tekleyohannes, M.K., Rybalkin, V., Ghaffar, M.M. et al. iDocChip: A Configurable Hardware Architecture for Historical Document Image Processing. Int J Parallel Prog 49, 253–284 (2021). https://doi.org/10.1007/s10766-020-00690-y.

- [23] Patel, S.K., Garg, B. & Rai, S.K. An Efficient Accuracy Reconfigurable CLA Adder Designs Using Complementary Logic. J Electron Test 36, 135–142 (2020). https://doi.org/10.1007/s10836-019-05851-7.

- [24] Khurshid, B., Mir, R.N. An Efficient FIR Filter Structure Based on Technology-Optimized Multiply-Adder Unit Targeting LUT-Based FPGAs. Circuits Syst Signal Process 36, 600–639 (2017). https://doi.org/10.1007/s00034-016-0312-9.

- [25] Bin Talib, G.H., El-Maleh, A.H. & Sait, S.M. Design of Fault Tolerant Adders: A Review. Arab J Sci Eng 43, 6667–6692 (2018). https://doi.org/10.10 07/s13369-018-3556-9.